# DIGITAL SIGNAL PROCESSING APPLICATIONS

**USING THE ADSP-2100 FAMILY**

DATA MEMORY 16K × 16

PERIPHERALS

PROGRAM MEMORY 16/32K × 24 DSP MICROPROCESSOR

CLOCK

# DIGITAL SIGNAL PROCESSING APPLICATIONS USING THE ADSP-2100 FAMILY

**VOLUME 2**

#### ANALOG DEVICES TECHNICAL REFERENCE BOOKS

#### Published by Prentice Hall

Analog-Digital Conversion Handbook Digital Signal Processing in VLSI Digital Signal Processing Applications Using the ADSP-2100 Family, Volumes 1 and 2 Digital Signal Processing Laboratory Using the ADSP-2101 Microcomputer ADSP-2100 Family User's Manual

#### Published by Analog Devices

Nonlinear Circuits Handbook Transducer Interfacing Handbook Synchro & Resolver Conversion High-Speed Design Seminar Mixed-Signal Design Seminar

# DIGITAL SIGNAL PROCESSING APPLICATIONS USING THE ADSP-2100 FAMILY

#### **VOLUME 2**

by

The Applications Engineering Staff of

Analog Devices, DSP Division

Edited by Jere Babst

P T R PRENTICE HALL Englewood Cliffs, New Jersey 07632

#### © 1995 by Analog Devices, Inc., Norwood, MA 02062

The publisher offers discounts on this book when ordered in bulk quantities. For more information, contact: Corporate Sales Department, P T R Prentice Hall, 113 Sylvan Ave., Englewood Cliffs, NJ 07632. Phone (201) 592-2863 Fax (201) 592-2249

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices, Inc., for its use.

Analog Devices, Inc., makes no representation that the interconnection of its circuits as described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith.

Specifications and prices are subject to change without notice.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

ISBN 0-13-178567-2

Prentice-Hall International (UK) Limited, London

Prentice-Hall of Australia Pty. Limited, Sydney

Prentice-Hall Canada Inc., Toronto

Prentice-Hall Hispanoamericana, S.A., Mexico

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Simon & Schuster Asia Pte. Ltd., Singapore

Editora Prentice-Hall do Brasil, Ltda., Rio de Janeiro

| CHAPT            | ER 1 INTRODUCTION                     |                 |

|------------------|---------------------------------------|-----------------|

| 1.1              | OVERVIEW                              | . 1             |

| 1.2              | ADSP-2100 FAMILY PROCESSORS           |                 |

| 1.2.1            | ADSP-2100 Family Base Architecture    | . 4             |

| 1.2.2            | ADSP-2101 Architecture                | . 7             |

| 1.2.3            | ADSP-2111 Architecture                | . 9             |

| 1.2.4            | ADSP-21msp50 Architecture             | 10              |

| 1.3              | ASSEMBLY LANGUAGE OVERVIEW            | 11              |

| 1.4              | DEVELOPMENT SYSTEM                    | 13              |

| 1.5              | CONVENTIONS OF NOTATION               | 14              |

| 1.6              | PROGRAMS ON DISK                      | 15              |

| 1.7              | FOR FURTHER SUPPORT                   | 15              |

| CHAPT            | <del></del>                           | 1.0             |

| 2.1              | OVERVIEW                              | $\frac{17}{17}$ |

| 2.2              | V.32 MODEM DEFINITION                 |                 |

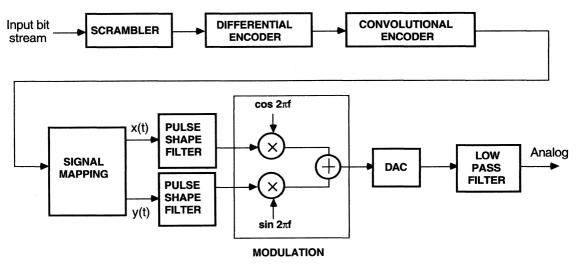

| 2.2.1            | Transmitter Algorithms                | 18              |

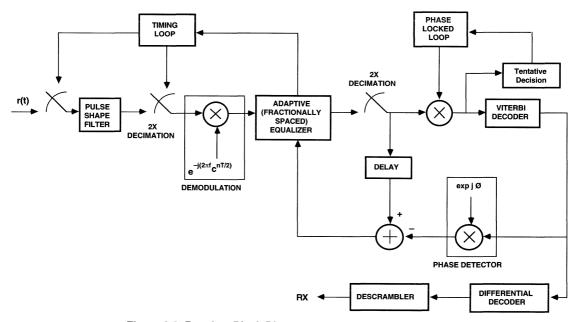

| 2.2.2            | Receiver Algorithms                   | 20<br>21        |

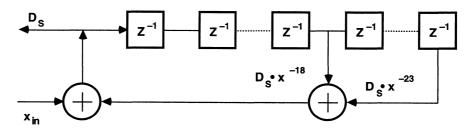

| 2.2.3            | Scrambler                             | 21              |

| 2.2.4            | Descrambling                          | 22              |

| 2.2.5            | ADSP-2100 Family Implementation       | 24<br>25        |

| 2.2.6            | Scrambler/Descrambler Programs        | 25<br>20        |

| 2.2.7            | Raised Cosine Filter                  | <i>32</i>       |

| 2.2.8            | ADSP-2100 Family Implementation       | 33<br>25        |

| 2.2.9            | Trellis Encoding                      | <i>37</i>       |

| 2.2.10           | ADSP-2100 Family Implementation       | 39<br>47        |

| 2.2.11           | Viterbi Decoding                      | 4/<br>50        |

| 2.2.12           | Data Constellation                    |                 |

| 2.2.13           | Viterbi Algorithm                     | ED<br>DU        |

| 2.2.14<br>2.2.15 | ADSP-2100 Family Implementation       | 52<br>52        |

| 2.2.15           | Shortest Path Through Trellis Diagram | J               |

| 2.2.16   | Viterbi Program                                                             | 55   |

|----------|-----------------------------------------------------------------------------|------|

| 2.2.16.1 | Initialization                                                              | 55   |

| 2.2.16.2 | Data Input & Euclidean Distance                                             | 55   |

| 2.2.16.3 | Shortest Path                                                               | 55   |

| 2.2.16.4 | Last Surviving Path                                                         | 55   |

| 2.2.16.5 | Determination Of Error Corrected Data                                       | 56   |

| 2.3      | QUADRATURE AMPLITUDE MODULATION                                             | 75   |

| 2.3.1    | OAM Methodology                                                             | 75   |

| 2.3.2    | ADSP-2100 Family Implementation                                             | 78   |

| 2.4      | ECHO CANCELLATION                                                           | 81   |

| 2.4.1    | Echo Cancellation AlgorithmADSP-2100 Family Implementation Of LMS Algorithm | 82   |

| 2.4.2    | ADSP-2100 Family Implementation Of LMS Algorithm                            | . 84 |

| 2.4.3    | Frequency Offset Compensation                                               | . 88 |

| 2.4.4    | Frequency Offset CompensationFamily Implementation Of Hilbert Transform     | . 91 |

| 2.4.5    | V.32 Modem Implementation                                                   | . 96 |

| 2.5      | ADAPTIVE EQUALİZATION                                                       | . 98 |

| 2.5.1    | History Of Adaptive Filters                                                 | . 98 |

| 2.5.2    | Applications Of Adaptive Filters                                            | . 99 |

| 2.5.3    | Channel Equalization In A Modem                                             | 101  |

| 2.5.3.1  | Equalization                                                                | 102  |

| 2.5.3.2  | Performance Index                                                           | 105  |

| 2.5.4    | Equalizer Architectures                                                     | 105  |

| 2.5.4.1  | Real Or Complex                                                             | 106  |

| 2.5.4.2  | Sampling Rates                                                              | 107  |

| 2.5.5    | Least Mean Squared (LMS) Algorithm                                          | 109  |

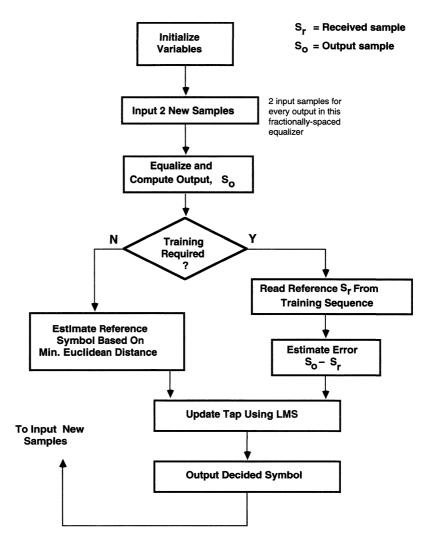

| 2.5.6    | Program Structure                                                           | 112  |

| 2.5.6.1  | Input New Sample                                                            | 113  |

| 2.5.6.2  | Filtering (Equalizing)                                                      | 113  |

| 2.5.6.3  | Training Sequence                                                           | 114  |

| 2.5.6.4  | Decision-Directed Adaptation                                                | 115  |

| 2.5.6.5  | Tap Update (LMS Algorithm)                                                  | 117  |

| 2.5.6.6  | Output                                                                      | 118  |

| 2.5.7    | Practical Considerations                                                    | 119  |

| 2.5.7.1  | Viterbi Decoder                                                             |      |

| 2.5.7.2  | Pseudo-Random Training Sequence                                             | 119  |

| 2.5.7.3  | Delay Line Length                                                           | 119  |

| 2.6      | CONTINUOÚS PHASE MODULATION                                                 | 120  |

| 2.6.1    | CPFSK Methodology                                                           | 120  |

| 2.6.2    | ADSP-2100 Family Implementation                                             | 121  |

| 2.7      | V.27 ter & V.29 MODEM TRANSMITTERS                                          | 126  |

| 2.7.1    | V.27 ter Transmitter                                                        | 126  |

| 2.7.2    | V.29 Transmitter                                                            | 141  |

| 2.8      | REFERENCES                                                                  |      |

| CHAPT    | ER 3 LINEAR PREDICTIVE CODING                    |     |

|----------|--------------------------------------------------|-----|

| 3.1      | OVERVIEW                                         | 157 |

| 3.2      | LINEAR PREDICTION                                | 157 |

| 3.3      | 7.8 kbits/s LPC                                  |     |

| 3.4      | 2.4 kbits/s LPC                                  | 163 |

| 3.5      | LPC SUBROUTINES                                  |     |

|          |                                                  |     |

| CHAPT    | ER 4 GSM CODEC                                   |     |

| 4.1      | OVERVIEW                                         | 205 |

| 4.1.1    | Speech Codec                                     | 205 |

| 4.1.2    | Software Comments                                | 206 |

| 4.1.2.1  | Multiply With Rounding                           | 206 |

| 4.1.2.2  | Arithmetic Saturation Results                    | 206 |

| 4.1.2.3  | Temporary Arrays                                 | 207 |

| 4.1.2.4  | Shared Subroutines                               | 207 |

| 4.2      | ENCODER                                          |     |

| 4.2.1    | Down Scaling & Offset Compensation Of The Input  | 208 |

| 4.2.2    | Pre-Emphasis Filtering                           | 208 |

| 4.2.3    | Auto-Correlation                                 | 209 |

| 4.2.4    | The Schur Recursion                              | 209 |

| 4.2.5    | Transformation Of The Reflection Coefficients    | 211 |

| 4.2.6    | Quantization & Coding Of Logarithmic-Area-Ratios | 212 |

| 4.2.7    | Decoding Of Logarithmic-Area-Ratios              | 212 |

| 4.2.8    | Short Term Analysis Filtering                    | 213 |

| 4.2.8.1  | Transformation Of The LARs Into Coefficients     | 214 |

| 4.2.8.2  | Short Term Analysis Filtering                    | 215 |

| 4.2.9    | Calculation Of The Long Term Parameters          | 215 |

| 4.2.9.1  | Long Term Analysis Filtering                     | 216 |

| 4.2.9.2  | Long Term Synthesis Filtering                    | 217 |

| 4.2.10   | Residual Pulse Excitation Encoding Section       | 217 |

| 4.2.10.1 | Weighting Filter                                 | 217 |

| 4.2.10.2 | Adaptive Sample Rate Decimation                  | 218 |

| 4.2.10.3 | APCM Quantization Of Selected Sequence           |     |

| 4.2.10.4 | APCM Inverse Quantization                        | 219 |

| 4.2.10.5 | Update Of The Short Term Residual Signal         | 219 |

| 4.3      | DECODER                                          | 220 |

| 4.3.1    | Short Term Synthesis Filtering                   | 220 |

| 4.3.1.1  | Short Term Synthesis Filter                      | 221 |

| 4.3.2    | Long Term Synthesis Filtering                    | 221 |

| 4.3.3    | Post Processing                                  | 222 |

| 4.4      | BENCHMARKS & MEMORY REQUIREMENTS                 | 222 |

| 45       | ISTINGS                                          | 223 |

| СНАРТ   | TER 5      | SUB-BAND ADPCM               |     |

|---------|------------|------------------------------|-----|

| 5.1     | OVERVIEW   |                              | 293 |

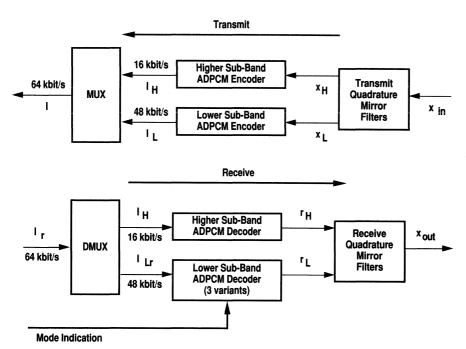

| 5.2     | SUB-BAND   | ADPCM ALGORITHM              | 294 |

| 5.3     | TRANSMIT   | `PATH                        | 294 |

| 5.3.1   | Transm     | nit Quadrature Mirror Filter | 294 |

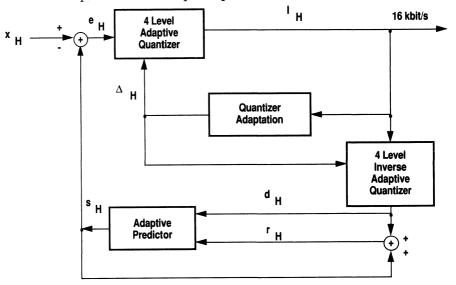

| 5.3.2   | Higher     | Sub-Band Encoder             | 296 |

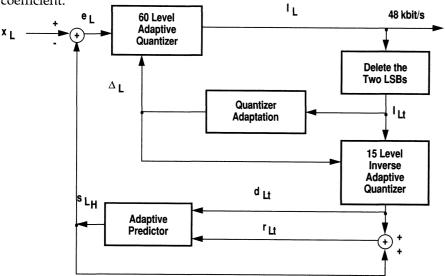

| 5.3.3   | Lower      | Sub-Band Encoder             | 296 |

| 5.4     | RECEIVE P. | ATH                          | 298 |

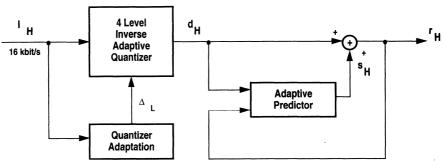

| 5.4.1   | Higher     | Sub-Band Decoder             | 298 |

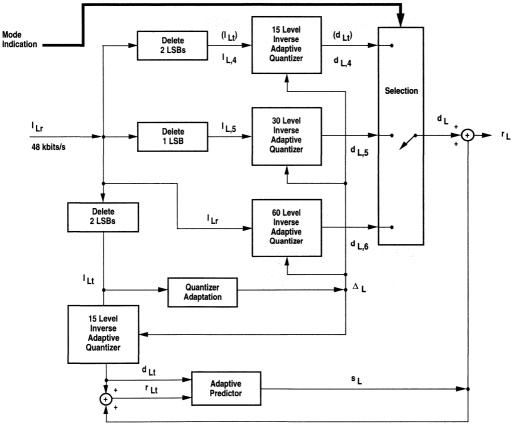

| 5.4.2   | Lower      | Sub-Band Decoder             | 299 |

| 5.4.3   | Receive    | Quadrature Mirror Filter     | 300 |

| 5.5     | ADSP-2100  | FAMILY IMPLEMENTATION        | 300 |

| 5.6     | SUBROUTI   | NE DESCRIPTIONS              | 301 |

| 5.6.1   | reset_m    | nem                          | 301 |

| 5.6.2   | filtez     |                              | 301 |

| 5.6.3   | filtep     |                              | 301 |

| 5.6.4   | quantl.    |                              | 301 |

| 5.6.5   | invqxl .   |                              | 302 |

| 5.6.6   | logscl     |                              | 302 |

| 5.6.7   |            |                              |     |

| 5.6.8   |            |                              |     |

| 5.6.9   | uppol2     |                              | 302 |

| 5.6.10  | uppol1     |                              | 302 |

| 5.6.11  |            |                              |     |

| 5.6.12  |            |                              |     |

| 5.6.13  | invqah     |                              | 303 |

| 5.6.14  | logsch.    |                              | 303 |

| 5.7     | BENCHMA    | RKS                          | 328 |

|         |            |                              |     |

| CHAPT   | ER 6       | SPEECH RECOGNITION           |     |

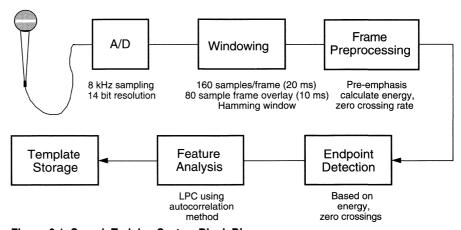

| 6.1     | OVERVIEW   | 7                            | 329 |

| 6.2     | SPEECH RE  | COGNITION SYSTEMS            | 330 |

| 6.2.1   | Voice P    | roduction & Modeling         | 330 |

| 6.2.2   | Trainin    | g Phase                      | 332 |

| 6.2.3   | Recogn     | ition Phase                  | 333 |

| 6.3     | SOFTWARE   | E IMPLEMENTATION             | 334 |

| 6.3.1   | Word A     | Acquisition & Analysis       | 335 |

| 6.3.1.1 | Red        | ceive Shell                  | 335 |

| 6.3.1.2 | Fra        | me Analysis                  | 336 |

| 6.3.1.3 | En         | dpoint Detection             | 337 |

|         |            |                              |     |

| 6.3.1.4 | Coefficient Conversion                  | 338 |

|---------|-----------------------------------------|-----|

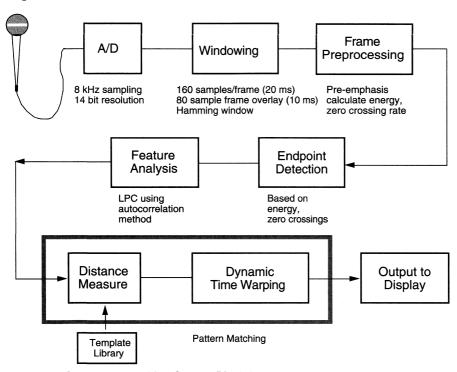

| 6.3.2   | Isolated Word Recognition               | 340 |

| 6.3.2.1 | Library Routines                        | 340 |

| 6.3.2.2 | Comparison                              | 341 |

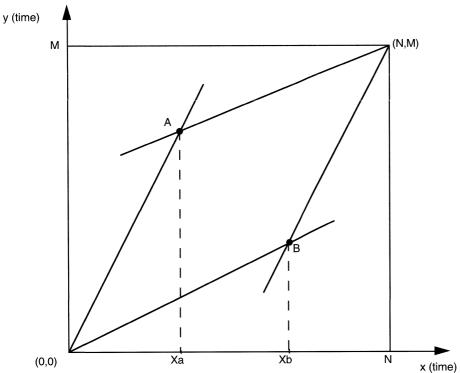

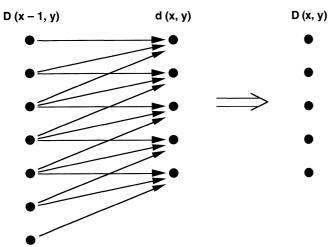

| 6.3.2.3 | Dynamic Time Warping                    | 342 |

| 6.3.2.4 | Ranking                                 | 346 |

| 6.3.3   | Main Shell Routines                     | 346 |

| 6.3.3.1 | Executive Shell                         |     |

| 6.3.3.2 | Demonstration Shell                     |     |

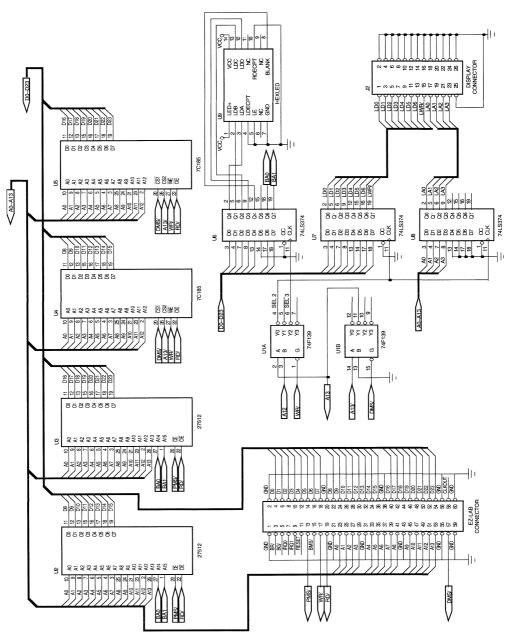

| 6.4     | HARDWARE IMPLEMENTATION                 |     |

| 6.5     | LISTINGS                                | 349 |

| 6.6     | REFERENCES                              |     |

|         |                                         |     |

| СНАРТ   | TER 7 DISCRETE COSINE TRANSFORM         |     |

| 7.1     | OVERVIEW                                | 443 |

| 7.2     | BACKGROUND                              |     |

| 7.3     | COMPUTATIONAL METHODS                   |     |

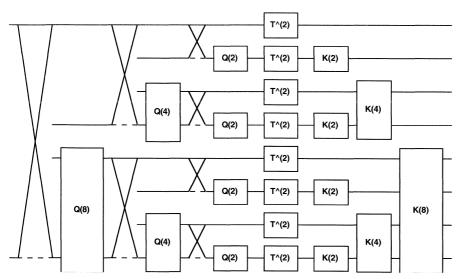

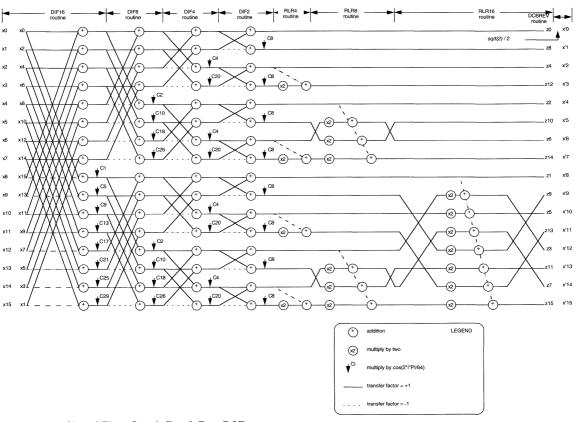

| 7.4     | HOU'S FAST DISCRETE COSINE ALGORITHM    | 449 |

| 7.5     | ZIG-ZAG SCANNING OF DCT COEFFICIENTS    | 453 |

| 7.6     | ZIG-ZAG SCANNING & ADSP-21XX PROCESSORS | 454 |

| 7.7     | LISTINGS                                |     |

| 7.8     | REFERENCES                              | 480 |

|         |                                         |     |

| CHAPT   | TER 8 DIGITAL TONE DETECTION            |     |

| 8.1     | OVERVIEW                                |     |

| 8.2     | IMPLEMENTATION                          |     |

| 8.2.1   | Choosing A Sampling Frequency           | 482 |

| 8.2.2   | Picking The Best Value Of N             | 483 |

| 8.2.2.1 | Leakage Loss                            | 483 |

| 8.2.2.2 | Frequency Resolution                    | 484 |

| 8.2.2.3 | Detection Time                          |     |

| 8.2.2.4 | Tone Detection Categories               |     |

| 8.2.2.5 | Tone Detection Example                  | 485 |

| 8.3     | BENCHMARKS FOR THE EXAMPLE PROGRAM      |     |

| 8.4     | LISTINGS                                | 490 |

| CHAPT                                                                                    | TER 9 DIGITAL CONTROL SYSTEM DESIGN       |                                        |

|------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------|

| 9.1                                                                                      | OVERVIEW                                  | 503                                    |

| 9.2                                                                                      | DIGITAL CONTROL SYSTEMS OVERVIEW          | 503                                    |

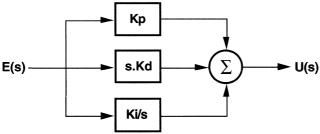

| 9.3                                                                                      | DIGITAL CONTROL SYSTEM MODEL              | 504                                    |

| 9.4                                                                                      | DIGITAL CONTROL SYSTEM HARDWARE           | 505                                    |

| 9.5                                                                                      | DIGITAL CONTROL SYSTEM SOFTWARE           | 507                                    |

| 9.6                                                                                      | DIGITAL PID CONTROLLER DESIGN             | 508                                    |

| 9.7                                                                                      | PID CONTROLLER IMPLEMENTATION             | 511                                    |

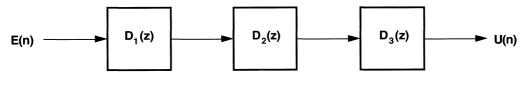

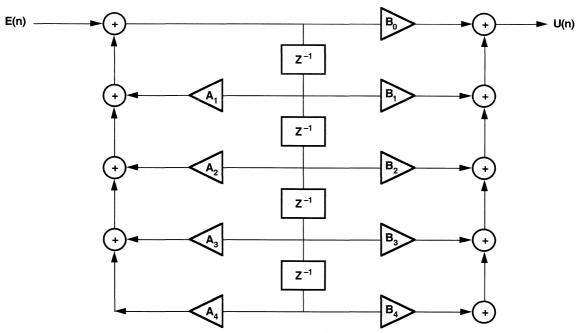

| 9.8                                                                                      | N'TH ORDER DIGITAL CONTROLLER DESIGN      | 513                                    |

| 9.8.1                                                                                    | Analog-Controller-Based Digital Design    | 513                                    |

| 9.8.2                                                                                    | Direct Digital Design                     | 514                                    |

| 9.8.3                                                                                    | State-Space Design                        | 515                                    |

| 9.9                                                                                      | N'TH ORDER DIGITAL CONTROLLER STRUCTURES  | 515                                    |

| 9.10                                                                                     | N'TH ORDER CONTROLLER IMPLEMENTATION      | 517                                    |

| 9.11                                                                                     | NOTCH FILTER EXAMPLE FOR THE ADSP-2100A   | 520                                    |

| 9.12                                                                                     | REFERENCES                                |                                        |

| 10.1<br>10.1.1<br>10.1.2<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4<br>10.3<br>10.4 | OVERVIEW                                  | 525<br>527<br>528<br>531<br>537<br>540 |

| СНАРТ                                                                                    |                                           |                                        |

| 11.1                                                                                     | OVERVIEW                                  | 551                                    |

| 11.2                                                                                     | HARDWARE                                  |                                        |

| 11.3                                                                                     | SOFTWARE                                  | 552                                    |

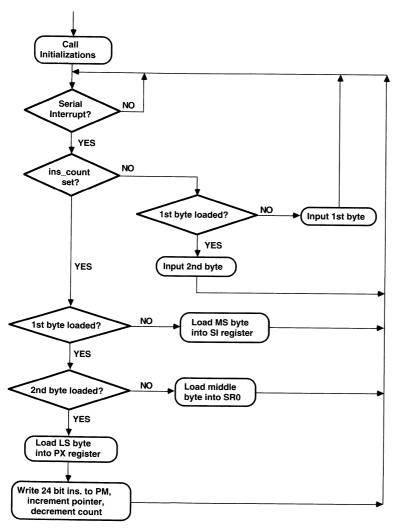

| 11.3.1                                                                                   | Program Flow                              | 553                                    |

| 11.3.2                                                                                   | Initialization & Timer Interrupt Routines | 554                                    |

| 11.3.3                                                                                   | Transmit & Receive Subroutines            | 563                                    |

| 11.4                                                                                     | BAUD RATES                                | 564                                    |

| 11.5                                                                                     | AUTOBAUD FEATURE                          | 564                                    |

| 11.6                                                                                     | CHARACTER ECHO EXAMPLE                    | 567                                    |

| 11.7                                                                                     | PROGRAM FILES                             | 569                                    |

#### CHAPTER 12 HARDWARE INTERFACING

| 12.1     | OVERVIEW                                                                                |     |

|----------|-----------------------------------------------------------------------------------------|-----|

| 12.2     | SOUNDPORT INTERFACES                                                                    |     |

| 12.2.1   | ADSP-2111/AD1849 SoundPort Interface                                                    |     |

| 12.2.2   | ADSP-2105/AD1849 SoundPort Interface                                                    |     |

| 12.2.3   | ADSP-2101/AD1847 SoundPort Interface                                                    |     |

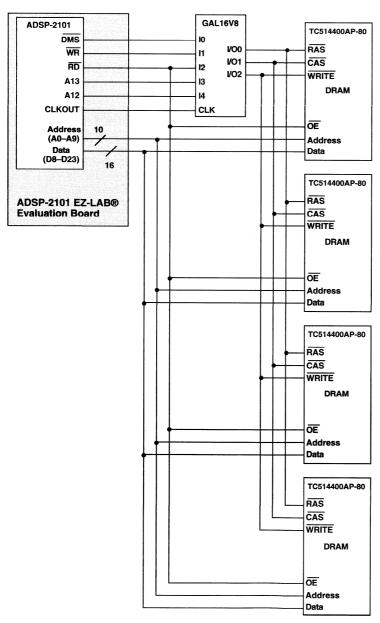

| 12.3     | INTERFACING DRAMS WITH THE ADSP-2100 FAMILY                                             | 603 |

| 12.3.1   | DRAM Configuration                                                                      | 606 |

| 12.3.2   | Multiplexed Memory Addressing                                                           | 607 |

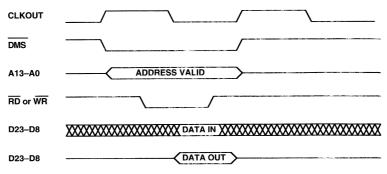

| 12.3.3   | DSP & DRAM Control Signals                                                              | 607 |

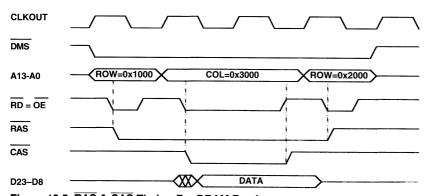

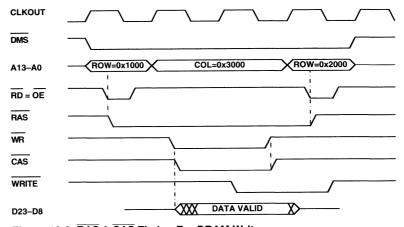

| 12.3.3.1 | DSP Read/Write Timing                                                                   | 607 |

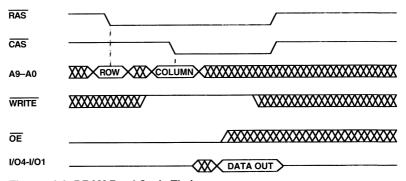

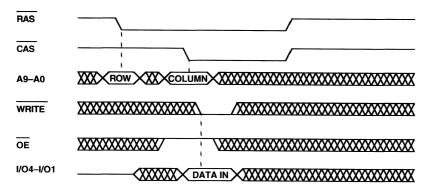

| 12.3.3.2 | DRAM Read/Write Timing                                                                  | 608 |

| 12.3.3.3 | RAS Generation                                                                          | 609 |

| 12.3.3.4 | CAS Generation                                                                          | 610 |

| 12.3.3.5 | WRITE & OE Generation                                                                   | 611 |

| 12.3.4   | DSP To DRAM Interface Timing                                                            |     |

| 12.3.4.1 | DRAM Read Timing                                                                        | 611 |

| 12.3.4.2 | DRAM Write Timing                                                                       | 612 |

| 12.3.5   | Memory Access Modes                                                                     | 613 |

| 12.3.5.1 | Page Mode                                                                               | 613 |

| 12.3.5.2 | Enhanced Or Fast Page Mode                                                              | 613 |

| 12.3.6   | DRAM Refresh                                                                            | 614 |

| 12.3.7   | DRAM Refresh Timing                                                                     | 615 |

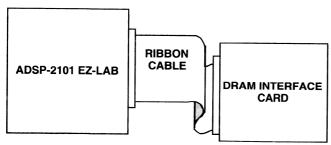

| 12.3.8   | EZ-LAB Implementation                                                                   | 617 |

| 12.3.9   | DRAM Program Listings                                                                   | 618 |

| 12.3.10  | DRAM Interfacing References                                                             | 630 |

| 12.4     | LOADING AN ADSP-2101 PROGRAM/SERIAL PORT                                                | 631 |

| 12.4.1   | A Monitor                                                                               | 631 |

| 12.4.2   | Implementation                                                                          | 632 |

| 12.5     | MEMORY INTERFACING FOR THE ADSP-2105                                                    | 637 |

| 12.5.1   | Ex System 1: Boot Pages For Program Memory                                              | 637 |

| 12.5.2   | Ex System 2: Booting With the -loader Option                                            | 638 |

| 12.5.3   | Ex System 2: Booting With the -loader Option<br>Ex System 3: Internal & External PM RAM | 639 |

| 12.5.4   | Ex System 4: Using External PM ROM                                                      | 640 |

| 12.5.5   | Hardware Implications                                                                   | 640 |

| 12.5.6   | Use Of The C-Compiler With ADSP-2105 Systems                                            | 641 |

| 12.5.7   | Linking Modules Generated By The C-Compiler                                             | 642 |

| 12.5.8   | Additional Suggestions                                                                  | 642 |

| 12.5.9   | About The Example Programs                                                              | 643 |

| 12.5.10  | Appendix: Example System 1                                                              |     |

#### **FIGURES**

| Figure 1.1  | ADSP-2100 Family Base Architecture              | 5     |

|-------------|-------------------------------------------------|-------|

| Figure 1.2  | ADSP-2101 Architecture                          | 8     |

| Figure 1.3  | ADSP-2111 Architecture                          | 10    |

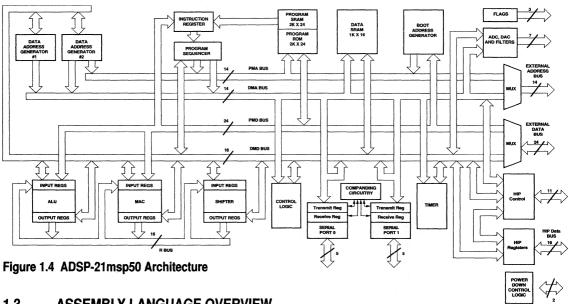

| Figure 1.4  | ADSP-21msp50 Architecture                       |       |

| Eigen 21    | Transmitter Plant Discussion                    | 10    |

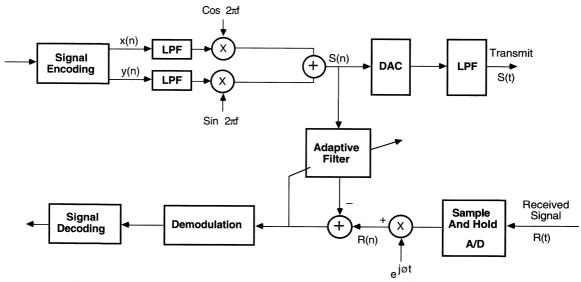

| Figure 2.1  | Transmitter Block Diagram                       | 19    |

| Figure 2.2  | Receiver Block Diagram                          | 20    |

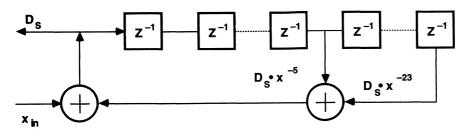

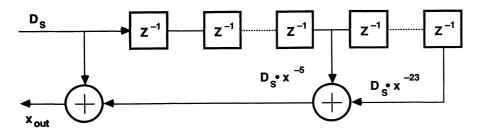

| Figure 2.3  | Call Mode Scrambler                             | 22    |

| Figure 2.4  | Answer Mode Scrambler                           | 23    |

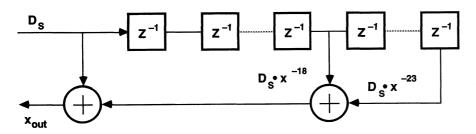

| Figure 2.5  | Call Mode Descrambler                           | 23    |

| Figure 2.6  | Answer Mode Descrambler                         |       |

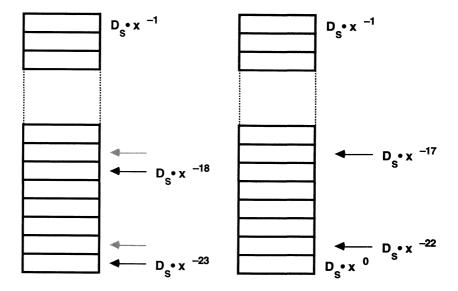

| Figure 2.7  | Circular Buffer Implementation For Scrambler    |       |

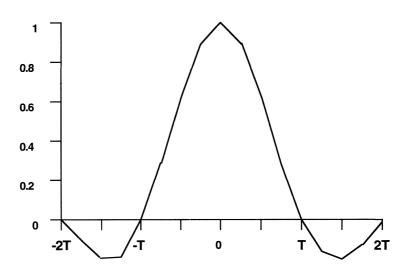

| Figure 2.8  | Raised Cosine Pulse Shaping Filter              | 34    |

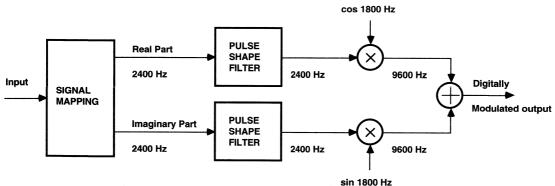

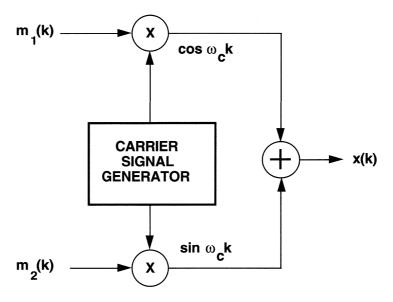

| Figure 2.9  | Modem Transmitter                               | 35    |

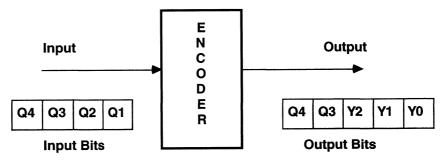

| Figure 2.10 | Encoder Block Diagram                           | 38    |

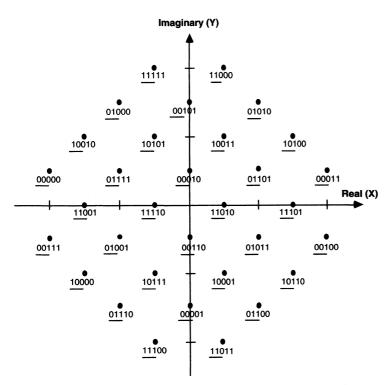

| Figure 2.11 | V.32 Signal Constellation                       |       |

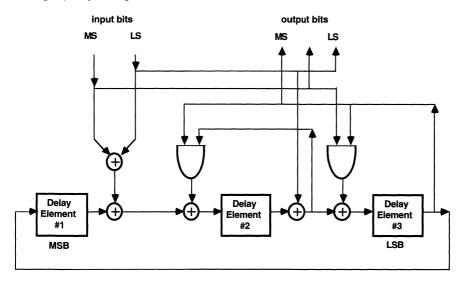

| Figure 2.12 | Convolutional Encoder Block Diagram             |       |

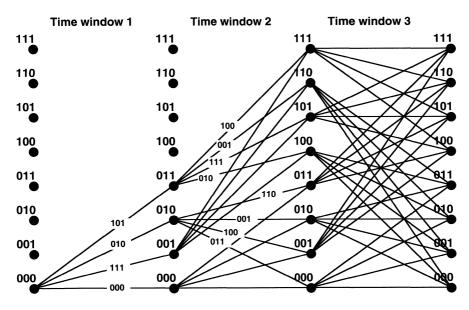

| Figure 2.13 | Trellis Diagram For Convolutional Encoding      |       |

| Figure 2.14 | Signal Constellation Showing Encoder Output     |       |

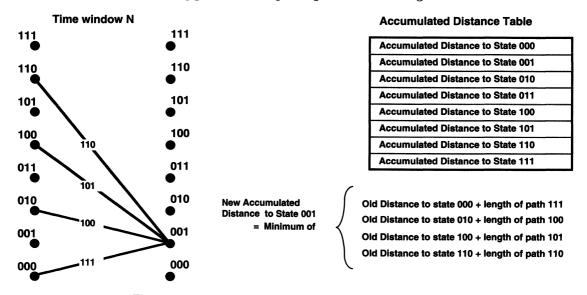

| Figure 2.15 | Accumulated Distance Table Update Example       | 54    |

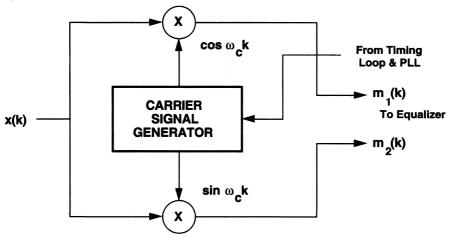

| Figure 2.16 | QAM Modulator Block Diagram                     | 76    |

| Figure 2.17 | QAM Demodulator Block Diagram                   | 77    |

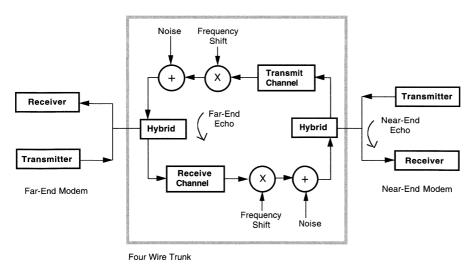

| Figure 2.18 | Telephone Channel Block Diagram                 | 81    |

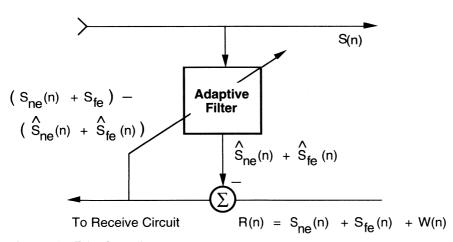

| Figure 2.19 | Echo Canceller                                  |       |

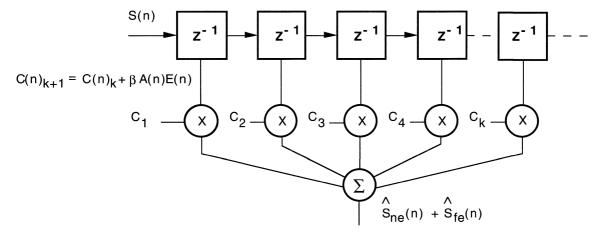

| Figure 2.20 | LMS Adaptive Filter                             | 84    |

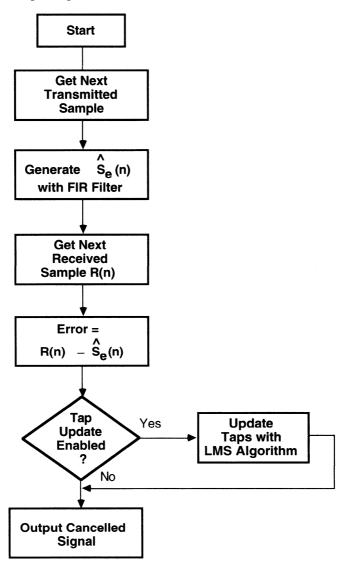

| Figure 2.21 | Flowchart For LMS Stochastic Gradient Algorithm | 85    |

| Figure 2.22 | Block Diagram Of Echo Canceller                 |       |

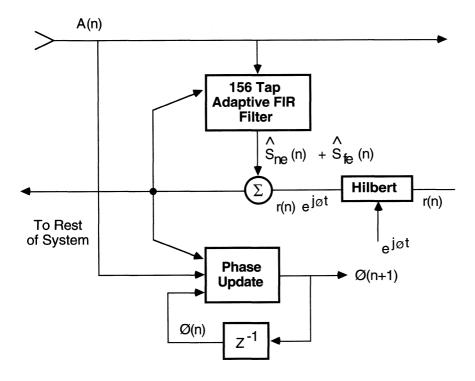

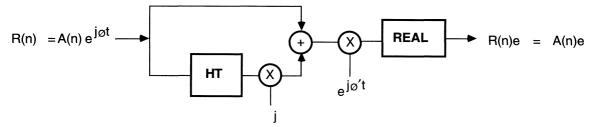

| Figure 2.23 | Block Diagram Of Hilbert Transform              | 90    |

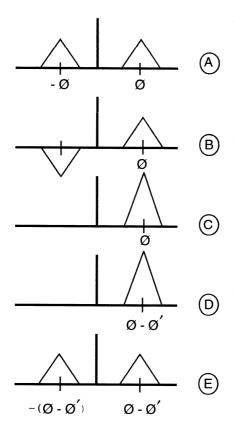

| Figure 2.24 | Spectrum Of Hilbert Frequency Shift             | 91    |

| Figure 2.25 | V.32 Modem Block Diagram                        |       |

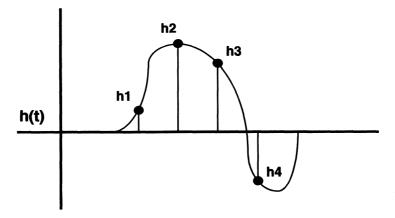

| Figure 2.26 | Example Short Impulse Response                  | . 102 |

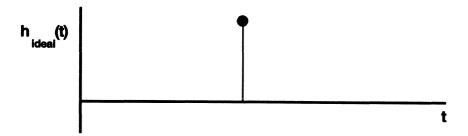

| Figure 2.27 | Pure Delay Impulse Response                     | . 103 |

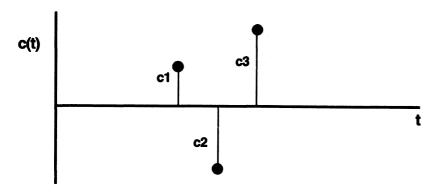

| Figure 2.28 | Equalizer Impulse Response                      |       |

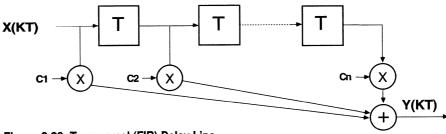

| Figure 2.29 | Transversal (FIR) Delay Line                    | . 106 |

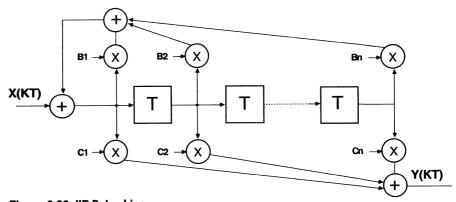

| Figure 2.30 | IIR Delay Line                                  |       |

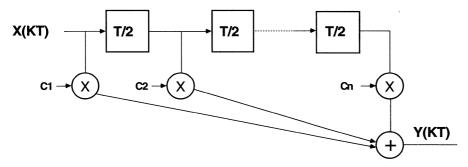

| Figure 2.31 | Fractionally Spaced Delay Line (FSE)            | . 107 |

| Figure 2.32 | Adaptive Equalizer Flowchart                    | . 112 |

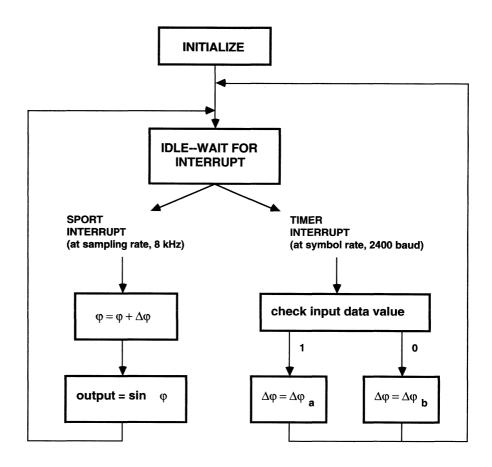

| Figure 2.33 | CPFSK Flow Diagram                              |       |

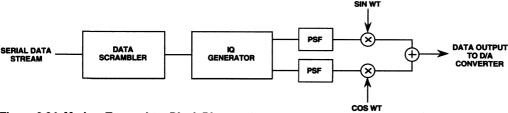

| Figure 2.34 | Modem Transmitter Block Diagram                 |       |

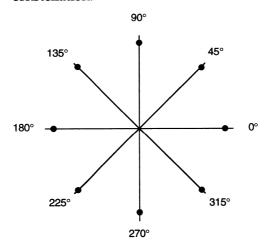

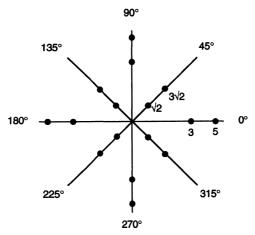

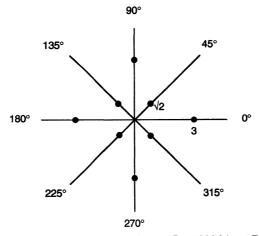

| Figure 2.35 | 8-Point V.27 <i>ter</i> Constellation           | . 128 |

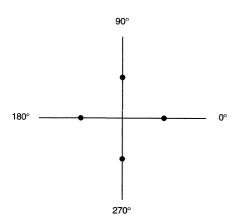

| Figure 2.36 | 4-Point V.27 ter Constellation                  |       |

| Figure 2.37 | V.29 Constellation                                       |

|-------------|----------------------------------------------------------|

| Figure 2.38 | V.29 Constellation For 7200 bits/s Fallback Mode 142     |

| Figure 2.39 | V.29 Constellation For 4800 bits/s Fallback Mode 143     |

| riguie 2.57 | V.27 Constellation 1 of 4000 bits/ 5 f another whose 110 |

| Figure 5.1  | Sub-Band ADPCM Algorithm Block Diagram 295               |

| Figure 5.2  | Higher Sub-Band Encoder Block Diagram                    |

| Figure 5.3  | Lower Sub-Band Encoder Block Diagram                     |

| Figure 5.4  | Higher Sub-Band Decoder Block Diagram                    |

| Figure 5.5  | Lower Sub-Band Decoder Block Diagram                     |

| rigure 5.5  | Lower out build becoder block blagfall                   |

| Figure 6.1  | Speech Training System Block Diagram                     |

| Figure 6.2  | Speech Recognition System Block Diagram                  |

| Figure 6.3  | Distance Matrix With Slope Constraints                   |

| Figure 6.4  | Time Warping Paths Between Sums & Distances 345          |

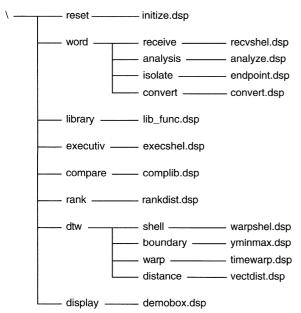

| Figure 6.5  | EXECSHEL.DSP Link File Menu Tree                         |

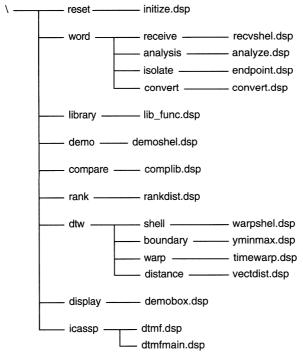

| Figure 6.6  | DEMOSHEL.DSP Link File Menu Tree348                      |

| Figure 6.7  | Speech Recognition System Circuit Board Schematic 350    |

| 1.80.10 011 | or                                                       |

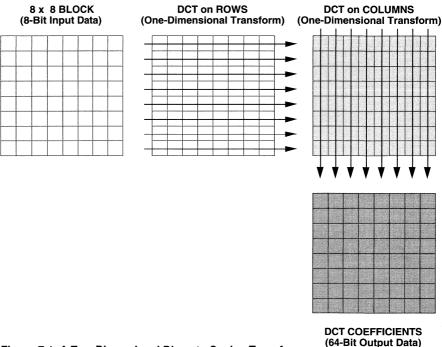

| Figure 7.1  | A Two-Dimensional Discrete Cosine Transform 444          |

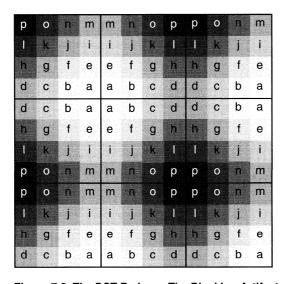

| Figure 7.2  | The DCT Reduces The Blocking Artifact 446                |

| Figure 7.3  | Implementation Of An N=16 DCT 451                        |

| Figure 7.4  | Signal Flow Graph For A Fast DCT452                      |

| Figure 7.5  | Zig-Zag Scanning Of Quantized Addresses 454              |

| O           |                                                          |

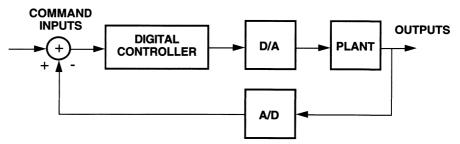

| Figure 9.1  | General Digital Control System 504                       |

| Figure 9.2  | Digital Control System Model 505                         |

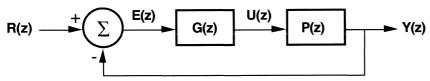

| Figure 9.3  | ADSP-2101-Based Actuator Controller 506                  |

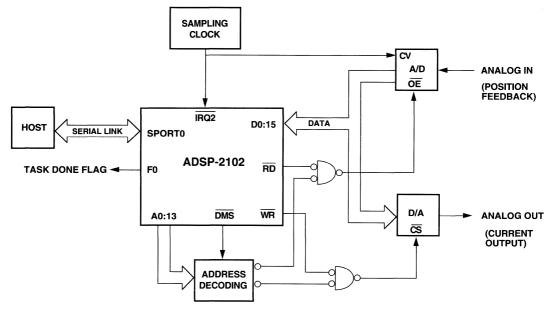

| Figure 9.4  | PID Block Diagram 509                                    |

| Figure 9.5  | PD, PI, & PID Controllers510                             |

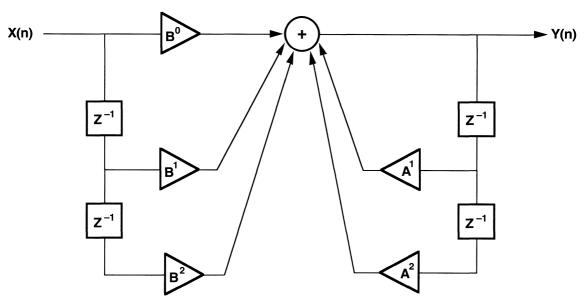

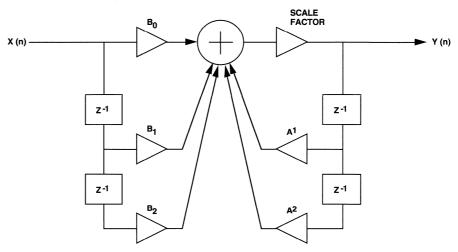

| Figure 9.6  | Second-Order Biquad Structure 515                        |

| Figure 9.7  | Cascaded Biquad Sections 516                             |

| Figure 9.8  | Fourth-Order Direct Form Controller 517                  |

|             |                                                          |

| Figure 10.1 | Second-Order Biquad IIR Filter Section                   |

| Figure 10.2 | Multiprecision Multiplication Of 32-Bit Numbers 530      |

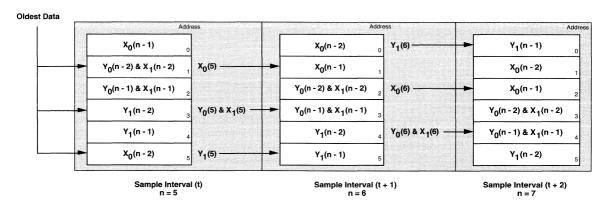

| Figure 10.3 | Modulo Addressing & Delay Line Data545                   |

| Figure 11 1 | General System Configuration 551                         |

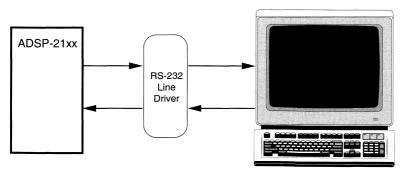

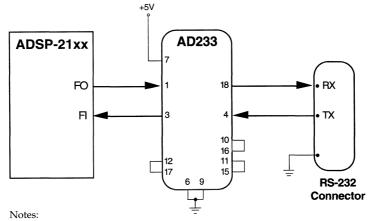

| Figure 11.1 | Example System Configuration 551                         |

| Figure 11.2 | Example System Configuration                             |

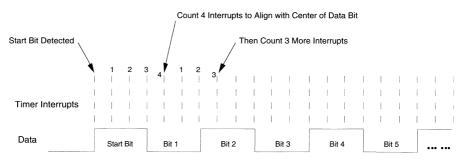

| Figure 11.3 | Receive Data Timing562                                   |

| Figure 12.1  | Functional Block Diagram Of DRAM Interface 605 |

|--------------|------------------------------------------------|

| Figure 12.2  | DSP Read/Write Timing                          |

| Figure 12.3  | DRAM Read Cycle Timing                         |

| Figure 12.4  | DRAM Delayed-Write Cycle Timing                |

| Figure 12.5  | RAS & CAS Timing For DRAM Read                 |

| Figure 12.6  | RAS & CAS Timing For DRAM Write                |

| Figure 12.7  | EZ-LAB/DRAM Interface Board Connection         |

| Figure 12.8  | Boot Program Flow Diagram                      |

|              | 8                                              |

|              |                                                |

| LISTINGS     |                                                |

| Listing 2.1  | Call Mode Scrambler Main Routine               |

| Listing 2.2  | Call Mode Scrambler Scrambling Routine         |

| Listing 2.3  | Call Mode Descrambler Routine                  |

| Listing 2.4  | Raised Cosine Filter                           |

| Listing 2.5  | Trellis Encoder Program                        |

| Listing 2.6  | Convolutional Encoder Routine                  |

| Listing 2.7  | Signal Mapping Routine                         |

| Listing 2.8  | Viterbi Decoder                                |

| Listing 2.9  | Modulator Code                                 |

| Listing 2.10 | Demodulator Code                               |

| Listing 2.11 | LMS Stochastic Gradient Implementation         |

| Listing 2.12 | Hilbert Transform Implementation               |

| Listing 2.13 | Delay Line Routine, Complex Tap Weights 108    |

| Listing 2.14 | LMS Routine                                    |

| Listing 2.15 | Input Routine                                  |

| Listing 2.16 | Filter Routine                                 |

| Listing 2.17 | Training Sequence Routine                      |

| Listing 2.18 | Decision-Directed Adaptation Routine 116       |

| Listing 2.19 | Tap Update Routine                             |

| Listing 2.20 | Output Routine 118                             |

| Listing 2.21 | CPFSK Program (ADSP-2101)                      |

| Listing 2.22 | Main V.27 <i>ter</i> Routine (MAIN27.DSP)      |

| Listing 2.23 | Data Acquisition Routine (GET27.DSP)134        |

| Listing 2.24 | Data Scrambler Routine (SCRAM27.DSP) 135       |

| Listing 2.25 | IQ Generator Routine (IQ27.DSP)                |

| Listing 2.26 | Pulse Shape Filter Routine (PSF.DSP)           |

| Listing 2.27 | Random Number Generator Routine (RAND.DSP) 139 |

| Listing 2.28 | Signal Modulation Routine (MODULATE.DSP) 140   |

| Listing 2.29 | Main V.29 Routine (MAIN29.DSP) 144             |

| Listing 2.30 | Data Acquisition Routine (GET29.DSP) 151       |

| Listing 2.31 | Data Scrambler Routine (SCRAM29.DSP) 152       |

| Listing 2.32 | IQ Generator Routine (IQ29.DSP)                |

| Listing 3.1  | 7.8 kbits/s LPC Routine                                                   | . 159 |

|--------------|---------------------------------------------------------------------------|-------|

| Listing 3.2  | 2.4 kbits/s LPC Routine                                                   | . 164 |

| Listing 3.3  | AUTOCOR.DSP Subroutine                                                    | . 169 |

| Listing 3.4  | DECODE.DSP Subroutine                                                     |       |

| Listing 3.5  | DEEMP.DSP Subroutine                                                      |       |

| Listing 3.6  | DURBIN.DSP Subroutine                                                     |       |

| Listing 3.7  | DURBIN2.DSP Subroutine                                                    | 180   |

| Listing 3.8  | ENCODE.DSP Subroutine                                                     |       |

| Listing 3.9  | GAIN.DSP Subroutine                                                       | . 189 |

| Listing 3.10 | OVERFLOW.DSP Subroutine                                                   | . 190 |

| Listing 3.11 | PITCH.DSP Subroutine                                                      | . 191 |

| Listing 3.12 | POLY.DSP Subroutine                                                       |       |

| Listing 3.13 | PREEMP.DSP Subroutine                                                     |       |

| Listing 3.14 | RANDOM.DSP Subroutine                                                     | 197   |

| Listing 3.15 | SQRT.DSP Subroutine                                                       | 198   |

| Listing 3.16 | SSYNTH.DSP Subroutine                                                     | 200   |

|              |                                                                           |       |

| Listing 4.1  | Initialization Routine (GSM_RSET.DSP)                                     | . 224 |

| Listing 4.2  | Codec Routine (GSM0610.DSP)                                               | . 228 |

| Listing 4.3  | Codec Routine (GSM0610.DSP)Voice Activity Detection Routine (GSM0632.DSP) | . 256 |

| Listing 4.4  | Comfort Noise Insertion Routine (GSM_SID.DSP)                             |       |

| Listing 4.5  | Discontinuous Trans Routine (GSM_DTX.DSP)                                 |       |

| Listing 4.6  | Data Acquisition Shell Routine (DMR21xx.DSP)                              |       |

|              | (,                                                                        |       |

| Listing 5.1  | Implementation Of The G.722 Algorithm                                     | . 304 |

| O            |                                                                           |       |

| Listing 6.1  | Executive Shell Subroutine (EXECSHEL.DSP)                                 | . 351 |

| Listing 6.2  | Demonstration Shell Subroutine (DEMOSHEL.DSP)                             | . 354 |

| Listing 6.3  | Data Variable Initialization Routine (INITIZE.DSP)                        |       |

| Listing 6.4  | Receive Word Routine (RECVSHEL.DSP)                                       | . 362 |

| Listing 6.5  | Frame Analysis Routine (ANALYZE.DSP)                                      | . 369 |

| Listing 6.6  | Endpoint Detection Routine (ENDPOINT.DSP)                                 | . 377 |

| Listing 6.7  | Coefficient Conversion Routine (CONVERT.DSP)                              | . 380 |

| Listing 6.8  | Library Functions Routine (LIB_FUNC.DSP)                                  |       |

| Listing 6.9  | Word Comparison Routine (COMPLIB.DSP)                                     |       |

| Listing 6.10 | Word Ranking Routine (RANKDIST.DSP)                                       |       |

| Listing 6.11 | Library Template Routine (WARPSHEL.DSP)                                   |       |

| Listing 6.12 | Y Coordinate Range Routine (YMINMAX.DSP)                                  |       |

| Listing 6.13 | Dynamic Time Warping Routine (TIMEWARP.DSP)                               | 418   |

| Listing 6.14 | Vector Distance Routine (VECTDIST.DSP)                                    | 422   |

| Listing 6.15 | Display Driver Routine (DEMOBOX.DSP)                                      | 425   |

| Listing 6.16 | DTMF Signal Generator Routine (DTMF.DSP)                                  | 431   |

| Listing 6.17 | Automatic Dialing Routine (DTMFMAIN DSP)                                  |       |

| Listing 7.1  | One-Dimensional Fast DCT (16 Points) Routine      | 456 |

|--------------|---------------------------------------------------|-----|

| Listing 7.2  | DIF16 Subroutine                                  |     |

| Listing 7.3  | DIF8 Subroutine                                   | 459 |

| Listing 7.4  | DIF4 Subroutine                                   | 460 |

| Listing 7.5  | DIF2 Subroutine                                   |     |

| Listing 7.6  | RLR4 Subroutine                                   |     |

| Listing 7.7  | RLR8 Subroutine                                   |     |

| Listing 7.8  | RLR16 Subroutine                                  |     |

| Listing 7.9  | DC_AND_BREV Subroutine                            |     |

| Listing 7.10 | Two-Dimensional Fast DCT (16 X 16 Points) Routine |     |

| Listing 7.11 | One-Dimensional Fast DCT (8 Points) Routine       |     |

| Listing 7.12 | DIF8_8 Subroutine                                 |     |

| Listing 7.13 | DIF4_8 Subroutine                                 | 473 |

| Listing 7.14 | DIF2_8 Subroutine                                 | 474 |

| Listing 7.15 | RLR4_8 Subroutine                                 |     |

| Listing 7.16 | RLR8_8 Subroutine                                 |     |

| Listing 7.17 | DC_AND_BREV_8 Subroutine                          | 477 |

| Listing 7.18 | Two-Dimensional Fast DCT (8 X 8 Points) Routine   | 478 |

| Listing 8.1  | Prime Factors Routine (FACTOR.C)                  | 491 |

| Listing 8.2  | Prime Numbers Routine (PRIMES.C)                  | 492 |

| Listing 8.3  | Best Sampling Frequency Routine (BESTFS.C)        | 493 |

| Listing 8.4  | Best Number Of Samples Routine (BESTN.C)          | 495 |

| Listing 8.5  | Coefficient Generating Routine (COEFGEN.C)        | 497 |

| Listing 8.6  | Tone Detection Routine (EXAMPLE.DSP)              | 499 |

| Listing 9.1  | PID_CONTROLLER Routine                            |     |

| Listing 9.2  | BIQUAD_CONTROLLER Routine                         |     |

| Listing 9.3  | NOTCH_FILTER Routine                              | 521 |

| Listing 10.1 | Basic Biquad Filter Subroutine                    | 526 |

| Listing 10.2 | Double-Precision Multiply Routine                 | 529 |

| Listing 10.3 | Double-Precision IIR Biquad Subroutine            |     |

| Listing 10.4 | Optimized Double-Precision IIR Biquad Subroutine  |     |

| Listing 10.5 | Half, Double-Precision IIR Biquad Subroutine      |     |

| Listing 10.6 | Half, Triple-Precision IIR Biquad Subroutine      | 540 |

| Listing 10.7 | Optimized Basic Biquad Filter Subroutine          | 545 |

| Listing 10.8 | Second-Level Optimization Of Basic Biquad Filter  | 547 |

| Listing 11.1 | UART.DSP Code                                     |     |

| Listing 11.2 | Autobaud Example Program                          |     |

| Listing 113  | Character Echo Program                            | 568 |

| Listing 12.1<br>Listing 12.2<br>Listing 12.3<br>Listing 12.4<br>Listing 12.5<br>Listing 12.6<br>Listing 12.7<br>Listing 12.8<br>Listing 12.9<br>Listing 12.10 | ADSP-2111/AD1849 Talk-Through Routine                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| TABLES                                                                                                                                                        |                                                                                    |

| Table 1.1                                                                                                                                                     | ADSP-2100 Family Functional Differences                                            |

| Table 2.1                                                                                                                                                     | Differential Encoder Lookup Table                                                  |

| Table 2.2                                                                                                                                                     | State Table For Convolutional Encoder                                              |

| Table 2.3                                                                                                                                                     | Lookup Table Of X & Y Coordinates                                                  |

| Table 2.3                                                                                                                                                     | ADSP-2100 Benchmarks For Echo Cancellation                                         |

|                                                                                                                                                               |                                                                                    |

| Table 2.5                                                                                                                                                     | 8-Point V.27 ter Phase Changes                                                     |

| Table 2.6                                                                                                                                                     | 4-Point V.27 ter Phase Changes                                                     |

| Table 2.7                                                                                                                                                     | 8-Point V.29 Phase Changes                                                         |

| Table 3.1                                                                                                                                                     | Parameter Set For The Sound Synthesis Model 158                                    |

| Table 4.1                                                                                                                                                     | GSM Implementation Benchmarks                                                      |

| Table 5.1                                                                                                                                                     | Decoder Modes Of Operation                                                         |

| Table 5.2                                                                                                                                                     | Inverse Adaptive Quantizer Modes Of Operation 300                                  |

| Table 5.3                                                                                                                                                     | Inverse Adaptive Quantizer Modes Of Operation 300<br>Typical Benchmark Performance |

| Tuble 0.0                                                                                                                                                     | Typical Deficiality 1 citofficance                                                 |

| Table 6.1                                                                                                                                                     | Time Warping Boundaries                                                            |

| Table 7.1                                                                                                                                                     | Cosine vs. Fourier Transform Characteristics 445                                   |

| Table 7.2                                                                                                                                                     | Benchmark Times For Executing The DCT 447                                          |

|                                                                                                                                                               | 201101111111111111111111111111111111111                                            |

| Table 8.1                                                                                                                                                     | Sample Frequencies & Prime Factors                                                 |

| Table 8.2                                                                                                                                                     | Sorted Sampling Frequencies (BESTFS.ERR)                                           |

| Table 8.3                                                                                                                                                     | Sorted Values For N (BESTN.ERR)                                                    |

| Table 8.4                                                                                                                                                     | Goertzel Coefficients 489                                                          |

|                                                                                                                                                               | Typical Benchmark Performance                                                      |

| Table 8.5                                                                                                                                                     | Typical benchmark Performance                                                      |

| Table 10.1 | Filter Routine Characteristics Summary | 549 |

|------------|----------------------------------------|-----|

| Гable 12.1 | Test System Components                 | 606 |

| INDEX      |                                        |     |

|            |                                        | 647 |

#### **Preface**

This book is the second volume of applications for the ADSP-2100 Family of Digital Signal Processors, and it is intended to complement, rather than replace the information contained in *Digital Signal Processing Applications Using the ADSP-2100 Family, Volume 1*. Each chapter embraces a single application topic, briefly describes the algorithm, and discusses its implementation on ADSP-2100 Family Processors. Although several topics contained in this book are addressed in Volume 1, the information presented here will provide you with a new perspective when approaching these topics.

If you want to understand how processors optimized for digital signal processing, such as the ADSP-2100 Family, are used to solve particular problems, you will find this book informative. The topics explored in this volume include, but are not limited to, telecommunications, hardware interfaces, and data encoding, decoding, and transmission.

This book does not provide full explanations of the signal processing theory behind the applications. The contributors and editor assumed that you already understand the theory and practice applying to your area of interest. *Digital Signal Processing in VLSI\**, a companion book in the Analog Devices technical reference set, provides much of the necessary basics. The references listed at the end of many of the chapters provide a wealth of additional information.

This volume includes solutions that vary in length and complexity. Here is a brief summary of each chapter's contents:

Introduction

Overviews of the ADSP-2100 Family base architecture, additional peripherals on the ADSP-2101, ADSP-2111, and ADSP-21msp50, assembly language, and development system.

Modems

Implementations for V.32, V.27 ter, and V.29 modems.

• Linear Predictive Coding

Techniques used to analyze, encode, and decode 7.8 kbits/s and 2.4 kbits/s speech signals.

<sup>\*</sup>Higgins, Richard J., Digital Signal Processing in VLSI. Englewood Cliffs, NJ: Prentice Hall 1990

GSM Codec

Implementation of the Pan-European Digital Mobile Radio (DMR) Speech Codec Specification 06.10. This chapter also includes subroutines for Voice Activity Detection (VAD, Specification 06.32) and Comfort Noise Insertion (CNI, Specification 06.12).

Sub-Band Adaptive Differential Pulse Code Modulation

Implementation of the CCITT Sub-band ADPCM Recommendation G.722.

• Speech Recognition

A design example and demonstration that implements a speech recognition system using the ADSP-2101 EZ-LAB Demonstration Board and an expansion board.

• Discrete Cosine Transform

Implementation of an algorithm that performs a Discrete Cosine Transform.

• Digital Tone Detection

Techniques for detecting digital representations of sinusoidal tones.

• Digital Control System Design

Several algorithms and software and hardware design methods and guidelines for high-speed digital control systems.

Variations On IIR Biquad Filters

Several variations on the basic IIR biquad filter that include multiprecision filters and optimized filter subroutines.

Software UART

Software implementation of a Universal Asynchronous Receiver/Transmitter.

Hardware Interfacing

Hardware and software interface solutions that include SoundPort® interfaces, a DRAM interface, loading a program through the serial port (SPORT), and a memory interface for the ADSP-2105.

#### **Acknowledgments**

The software and hardware implementations and the accompanying text for this book were provided by the Applications Engineering group of Analog Devices SPD Division. They designed, developed, and tested the solutions presented here and reviewed the final publication. Besides Jerry McGuire, who leads the group, contributors included: Dan Ash, Chris Cavigioli, Gordon Cooper, Ron Coughlin, Jeff Cuthbert, Colin Duggin, Kapriel Karagozyan, Noam Levine, Ann Mascarin, and Bruce Wolfeld.

Bob Fine and Jerry McGuire helped compile the index and provided editorial feedback on every chapter; Adele Hastings produced the layout, assisted with the illustrations, and assembled the finished book; Christine Hulme collected, compiled, and tested the code to produce the final diskette.

Norwood, Massachusetts

Jere Babst

# 1

#### 1.1 OVERVIEW

This book is the second volume of digital signal processing applications based on the ADSP-2100 DSP microprocessor family. It contains a compilation of routines for a variety of common digital signal processing applications. As in the first volume, you may use these routines without modification or you can use them as a starting point for the development of routines tailored to your particular needs.

Besides showing the specific applications, these routines demonstrate a variety of programming techniques for getting the most performance out of the ADSP-2100 family processors. For example, several routines show you how to use address pointers efficiently to address circular buffers. We believe that you will benefit from reading every chapter, even if your present application uses only a single topic.

Some material in this book was originally published in an applications handbook that featured modem routines. The information in that volume was updated and integrated into this book, which supersedes the earlier publication.

#### 1.2 ADSP-2100 FAMILY PROCESSORS

This section briefly describes the ADSP-2100 family of processors. For complete information, refer to the *ADSP-2100 Family User's Manual*, (ISBN 0-13-006958-2) available from Prentice Hall and Analog Devices. For the applications in this book, "ADSP-2100" refers to *any* processor in the ADSP-2100 family unless otherwise noted. At the time of publication, the ADSP-2100 Family consisted of the following members:

- ADSP-2100A—DSP microprocessor with off-chip Harvard architecture

- ADSP-2101—DSP microcomputer with on-chip program and data memory

- ADSP-2103—Low-voltage microcomputer, 3.3-volt version of ADSP-2101

- ADSP-2105—Low-cost DSP microcomputer

- ADSP-2111—DSP microcomputer with Host Interface Port

- ADSP-2115—High-performance, Low-cost DSP microcomputer

- ADSP-2161/62/63/64—Custom ROM-programmed DSP microcomputers

- ADSP-2165/66—Custom ROM-programmed DSP microcomputers with larger on-chip memories and powerdown

- ADSP-21msp5x—Mixed-Signal DSP microcomputers with integrated, on-chip analog interface and powerdown

- ADSP-2171—Enhanced ADSP-2100 Family processor offering 33 MIPS performance, host interface port, powerdown, and instruction set extensions for bit manipulation, multiplication, biased rounding, and global interrupt masking

Since Analog Devices strives to provide products that exploit the latest technology, new family members will be added to this list periodically. Please contact your local Analog Devices sales office or distributor for a complete list of available products.

The ADSP-2100A is a programmable single-chip *microprocessor* optimized for digital signal processing and other high-speed numeric processing applications. The ADSP-2100A contains an ALU, a multiplier/accumulator (MAC), a barrel shifter, two data address generators and a program sequencer. It features an off-chip Harvard architecture, where data and program buses are available to external memories and devices.

The ADSP-2101 is a programmable single-chip *microcomputer* based on the ADSP-2100A. Like the ADSP-2100A, the ADSP-2101 contains computational units, as well as a program sequencer and dual address generators; these elements, combined with internal data and address busses, comprise the base architecture of the ADSP-2100 Family microcomputers. Additionally, all family members have the following core features:

- on-chip data memory, program memory, and boot memory

- one or two serial ports

- a programmable timer

- and enhanced interrupt capabilities.

To expand the usefulness of the ADSP-2100 Family, the base architecture has been enhanced with a variety of memory configurations, peripheral devices, and features for improved performance. Table 1.1 is a matrix that identifies the functional differences between members of the ADSP-2100 Family.

| Model         | Instruction<br>Cycle Time<br>ns | Internal<br>Program<br>Memory | Internal<br>Data<br>Memory | Host<br>Interface<br>Port | Program<br>Memory<br>Boot | Serial<br>Ports | Programmable<br>Timer | On-chip<br>A/D & D/A | External<br>Interrupts | Low Power<br>Modes | Pin<br>Count |

|---------------|---------------------------------|-------------------------------|----------------------------|---------------------------|---------------------------|-----------------|-----------------------|----------------------|------------------------|--------------------|--------------|

| ADSP-2100A    | 80                              | CACHE                         | <u> </u>                   | · ·                       | · <u>—</u>                | _               | _                     | . —                  | 4                      | _                  | 100          |

| ADSP-2101     | 50                              | 2k x 24                       | 1K X 16                    | · <u></u>                 | $\checkmark$              | 2               | $\sqrt{}$             | _                    | 3                      | 1                  | 80/68        |

| ADSP-2102     | 50                              | 2k x 24<br>RAM/ROM            | 1K X 16                    |                           | √                         | 2               | √ v                   |                      | 3                      | 1                  | 80/68        |

| ADSP-2103(3 V | 77                              | 2k x 24                       | 1K X 16                    | -                         | √ ,                       | 2               | . 1                   |                      | 3                      | 1                  | 80/68        |

| ADSP-2105     | 100                             | 1k x 24                       | 0.5K X 16                  | _                         | √                         | 1               | √                     |                      | 3                      | 1                  | 68           |

| ADSP-2111     | 50                              | 2k x 24                       | 1K X 16                    | √                         | √ .                       | 2               | $\checkmark$          | _                    | 3                      | 1                  | 100          |

| ADSP-2115     | 50                              | 1k x 24                       | 0.5K X 16                  |                           | √                         | 2               |                       | · <u>-</u>           | 3                      | 1                  | 80/68        |

| ADSP-21msp50  | )A 77                           | 2k x 24                       | 1K X 16                    | $\checkmark$              | $\checkmark$              | 2               | √                     | √ ·                  | 3                      | 2                  | 144          |

| ADSP-21msp55  | 5A 77                           | 2k x 24                       | 1K X 16                    | $\checkmark$              | $\sqrt{}$                 | 2               | √                     | $\checkmark$         | 3                      | 2                  | 100          |

| ADSP-21msp56  | 6A 77                           | 2k x 24 &<br>2k x 24 ROM      | 1K X 16                    | . √                       | $\checkmark$              | 2               | √ √                   | $\checkmark$         | 3                      | 2                  | 100          |

| ADSP-2161     | 60                              | 8k x 24 ROM                   | 0.5K X 16                  | _                         | $\checkmark$              | 2               | $\checkmark$          | _                    | 3                      | 1                  | 80/68        |

| ADSP-2162(3 V | ') 100                          | 8k x 24 ROM                   | 0.5K X 16                  | _                         | $\checkmark$              | 2               | $\checkmark$          | _                    | 3                      | 1                  | 80/68        |

| ADSP-2163     | 60                              | 2k x 24 ROM                   | 0.5K X 16                  |                           | $\checkmark$              | 2               | <b>V</b>              |                      | 3                      | 1                  | 80/68        |

| ADSP-2164(3 V | ') 100                          | 2k x 24 ROM                   | 0.5K X 16                  | _                         | $\checkmark$              | 2               | √                     |                      | 3                      | 1                  | 80/68        |

| ADSP-2165     | 60                              | 1K X 24 RAM<br>12k x 24 ROM   | 4K X 16                    | ·                         | $\sqrt{}$                 | 2               | <b>V</b>              | <u> </u>             | 3                      | 1                  | 80           |

| ADSP-2166(3 V | ') 100                          | 2k x 24 ROM                   | 0.5K X 16                  | _                         | $\checkmark$              | 2               | $\checkmark$          | _                    | 3                      | 1                  | 80           |

| ADSP-2171     | 30                              | 2k x 24 RAM<br>8k x 24 ROM    | 2K X 16                    | <b>V</b>                  | V                         | 2               | $\checkmark$          | . —                  | 3                      | 1                  | 128          |

|               |                                 |                               |                            |                           |                           |                 |                       |                      |                        |                    |              |

Table 1.1 ADSP-2100 Family Functional Differences

This chapter includes overviews of the ADSP-2100 family base architecture and the three family members that exhibit the most distinct features. These overviews include the following ADSP-2100 Family members:

- ADSP-2100 Family Base Architecture—contains the computational units, address generators, and program sequencer

- ADSP-2101–contains the base architecture, plus on-chip memory (program, data, and boot memory), a programmable timer, and enhanced interrupts

- ADSP-2111–contains the features of the ADSP-2101, plus a host interface port (HIP)

- ADSP-21msp50—contains the features of the ADSP-2101, plus a host interface port (HIP) and a voice-band analog front end

Other family members are variations on these DSPs. For example, the ADSP-2105 is based on the ADSP-2101, but it has less on-chip memory and only one serial port; the ADSP-2171 is similar to the ADSP-2111, except it has functional enhancements (low-power operation and expanded instruction set).

Because all the microcomputers of the ADSP-2100 family are code-compatible, the programs in this book can be executed on any DSP in the family, although some modifications for interrupt vectors, peripherals, and control registers may be necessary. All the programs in this book, however, are not designed to use the extra features and functions of some family members.

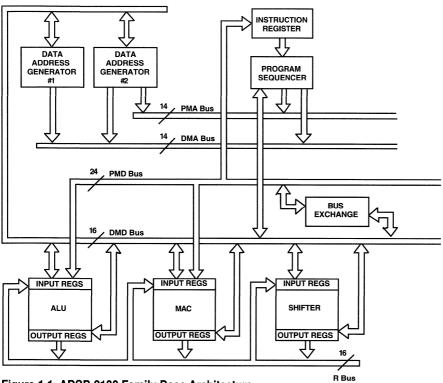

#### 1.2.1 ADSP-2100 Family Base Architecture

This section gives a broad overview of the ADSP-2100 family base architecture (shown in Figure 1.1). Refer to the *ADSP-2100 Family User's Manual* for additional details.

The base architecture contains three full-function and independent computational units: an arithmetic/logic unit, a multiplier/accumulator and a barrel shifter. The computational units process 16-bit data directly and provide for multiprecision computation.

Figure 1.1 ADSP-2100 Family Base Architecture

A program sequencer and two dedicated data address generators (used to simultaneously access data in two locations) supply addresses to memory. The sequencer supports single-cycle conditional branching and executes program loops with zero overhead. Dual address generators allow the processor to output simultaneous addresses for dual operand fetches. Together the sequencer and data address generators allow computational operations to execute with maximum efficiency. The ADSP-2100 family uses an enhanced Harvard architecture in which data memory stores data, and program memory stores instructions and data. This feature lets ADSP-2100 family processors fetch two operands on the same instruction cycle.

Five internal buses support the internal components.

- Program Memory Address (PMA) bus

- Program Memory Data (PMD) bus

- Data Memory Address (DMA) bus

- Data Memory Data (DMD) bus

- Result (R) bus (which interconnects the computational units)

The program memory data (PMD) bus serves primarily to transfer instructions from program memory to the instruction register. Instructions are fetched and loaded into the instruction register during one processor cycle; they execute during the following cycle while the next instruction is being fetched. The instruction register introduces a single level of pipelining in the program flow.

The next instruction address is generated by the program sequencer depending on the current instruction and internal processor status. This address is placed on the program memory address (PMA) bus. The program sequencer uses features such as conditional branching, loop counters and zero-overhead looping to minimize program flow overhead. The program memory address (PMA) bus is 14 bits wide, allowing direct access to up to 16K words of instruction code and data.

The data memory address (DMA) bus is 14 bits wide allowing direct access of up to 16K words of data. The data memory data (DMD) bus is 16 bits wide. The data memory data (DMD) bus provides a path for the contents of any register in the processor to be transferred to any other register, or to any data memory location, *in a single cycle*. The data memory address can come from two sources: an absolute value specified in the instruction code (direct addressing) or the output of a data address generator (indirect addressing). Only indirect addressing is supported for data fetches through the program memory bus.

The program memory data (PMD) bus can also be used to transfer data to and from the computational units through direct paths or through the PMD-DMD bus exchange unit. The PMD-DMD bus exchange unit permits data to be passed from one bus to the other. It contains hardware to overcome the 8-bit width discrepancy between the two buses when necessary.

Each computational unit contains a set of dedicated input and output registers. Computational operations generally take their operands from input registers and load the result into an output register. The

computational units are arranged in parallel rather than cascaded. To avoid excessive delays when a series of different operations is performed, the internal result (R) bus allows any of the output registers to be used directly (without delay) as the input to another computation.

There are two independent data address generators (DAGs). As a pair, they allow the simultaneous fetch of data stored in program and in data memory for executing dual-operand instructions in a single cycle. One data address generator (DAG1) can supply addresses to the data memory only; the other (DAG2) can supply addresses to either the data memory or the program memory. Each DAG can handle linear addressing as well as modulo addressing for circular buffers.

With its multiple bus structure, the ADSP-2100 family architecture supports a high degree of operational parallelism. In a single cycle, a family processor can fetch an instruction, compute the next instruction address, perform one or two data transfers, update one or two data address pointers and perform a computation. Every instruction can be executed in a single cycle.

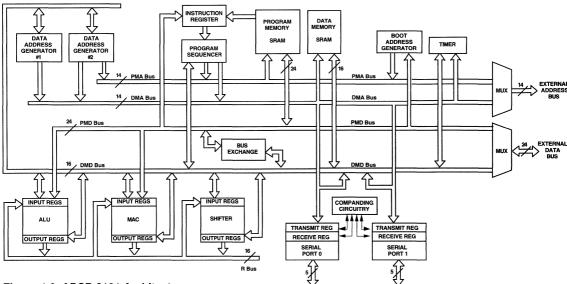

#### 1.2.2 ADSP-2101 Architecture

Figure 1.2 shows the architecture of the ADSP-2101 processor. In addition to the base architecture, the ADSP-2101 has two serial ports, a programmable timer, enhance interrupts, and internal program, data and boot memory.

The ADSP-2101 has 1K words of 16-bit data memory on-chip and 2K words of 24-bit program memory on-chip. The processor can fetch an operand from on-chip data memory, an operand from on-chip program memory and the next instruction from on-chip program memory in a single cycle.

This scheme is extended off-chip through a single external memory address bus and data bus that may be used for either program or data memory access and for booting. Consequently, the processor can access external memory once in any cycle.

Boot circuitry provides for loading on-chip program memory automatically after reset. Wait states are generated automatically for interfacing to a single low-cost EPROM. Multiple programs can be selected and loaded from the EPROM with no additional hardware.

Figure 1.2 ADSP-2101 Architecture

The memory interface supports memory-mapped peripherals with programmable wait-state generation. External devices can gain control of buses with bus request and grant signals ( $\overline{BR}$  and  $\overline{BG}$ ). An optional execution mode allows the ADSP-2101 to continue running from internal memory while the buses are granted to another master as long as an external memory operation is not required.

The ADSP-2101 can respond to six user interrupts. There can be up to three external interrupts, configured as edge- or level-sensitive. Internal interrupts can be generated from the timer and the serial ports. There is also a master RESET signal.

The two serial ports ("SPORTs") provide a synchronous serial interface; they interface easily and directly to a wide variety of popular serial devices. They have hardware companding (data compression and expansion) with both  $\mu\text{-law}$  and A-law available. Each port can generate an internal programmable clock or accept an external clock.

The SPORTs are synchronous and use framing signals to control data flow. Each SPORT can generate its serial clock internally or use an external clock. The framing synchronization signals may be generated internally or

by an external device. Word lengths may vary from three to sixteen bits. One SPORT (SPORT0) has a multichannel capability that allows the receiving or transmitting of arbitrary data words from a 24-word or 32-word bitstream. The SPORT1 pins have alternate functions and can be configured as two additional external interrupt pins and Flag Out (FO) and Flag In (FI).

The programmable interval timer provides periodic interrupt generation. An 8-bit prescaler register allows the timer to decrement a 16-bit count register over a range from each cycle to every 256 cycles. An interrupt is generated when this count register reaches zero. The count register is automatically reloaded from a 16-bit period register, and the count resumes immediately.

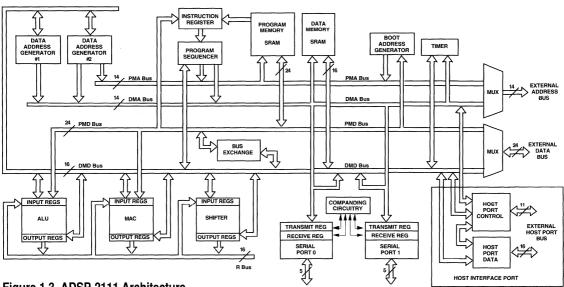

#### 1.2.3 ADSP-2111 Architecture

Figure 1.3 shows the architecture of the ADSP-2111 processor. The ADSP-2111 contains the same architecture of the ADSP-2101—plus a host interface port (HIP). This section only contains a brief overview; for detailed descriptions of the HIP and its operation, refer to the ADSP-2111 data sheet and *ADSP-2100 Family User's Manual*.

The host interface port is a parallel I/O port that lets the DSP act as a memory mapped peripheral (slave DSP) to a host computer or processor. You can think of the host interface port as a collection of dual-ported memory, or mailbox registers, that let the host processor communicate with the DSP's processor core. The host computer addresses the HIP as a section of 8-bit or 16-bit words of memory. To the processor core, the HIP is a group of eight data mapped registers.

The host interface port is completely asynchronous. This means that the host computer can write data into the HIP while the ADSP-2111 is operating at full speed.

The ADSP-2111 supports two types of booting operations. One method boots the DSP from external memory (usually an EPROM) through the boot memory interface. The ADSP-2100 Family User's Manual describes the boot memory interface in detail. In the second method, a boot program is loaded from the host computer through the HIP. Chapter 12, Hardware Interface includes a sample of code to load a program through the HIP.

Figure 1.3 ADSP-2111 Architecture

#### 1.2.4 ADSP-21msp50 Architecture

Figure 1.4 shows the architecture of the ADSP-21msp50 processor The ADSP-21msp50 contains the same core architecture of the ADSP-2101—plus a host interface port (described in the previous section) and an analog interface. This section only contains a brief overview; for detailed descriptions of the analog interface and its operation, refer to the ADSP-21msp50 data sheet and *ADSP-2100 Family User's Manual*.

The ADSP-21msp50 has an analog interface that provides the following features:

- linear-coded 16-bit sigma-delta ADC

- linear-coded 16-bit sigma-delta DAC

- on-chip anti-aliasing and anti-imaging filters

- individual interrupts for the ADC and DAC

- 8 kHz sampling frequency

- programmable gain for DAC and ADC

- on-chip voltage reference

The analog interface is configured and operated through several memory mapped control and data registers. The ADC and DAC I/O can be transmitted and received through individual memory mapped registers, or the data can be autobuffered directly into the processor's data memory.

#### 1.3 ASSEMBLY LANGUAGE OVERVIEW